Quartus II

v15.0官方正式版- 軟件大小:23.03KB

- 軟件語言:簡體中文

- 更新時間:2024-01-07

- 軟件類型:國產(chǎn)軟件 / 機械電子

- 運行環(huán)境:winall/win7/win10/win11

- 軟件授權(quán):免費軟件

- 官方主頁:http://www.jlass.com.cn

- 軟件等級 :

- 軟件廠商:暫無

- 介紹說明

- 下載地址

- 精品推薦

- 相關(guān)軟件

- 網(wǎng)友評論

Quartus II 官方版是Altera公司的綜合性PLD/FPGA開發(fā)軟件,支持原理圖、VHDL、VerilogHDL以及AHDL等多種設(shè)計輸入形式,內(nèi)嵌自有的綜合器以及仿真器,可以完成從設(shè)計輸入到硬件配置的完整PLD設(shè)計流程。而且Quartus II 官方版還具有速度快,界面統(tǒng)一,功能集中,易學(xué)易用等特點,讓用戶可以用的更加舒適。

Quartus II 官方版是Altera公司的綜合性PLD/FPGA開發(fā)軟件,支持原理圖、VHDL、VerilogHDL以及AHDL等多種設(shè)計輸入形式,內(nèi)嵌自有的綜合器以及仿真器,可以完成從設(shè)計輸入到硬件配置的完整PLD設(shè)計流程。而且Quartus II 官方版還具有速度快,界面統(tǒng)一,功能集中,易學(xué)易用等特點,讓用戶可以用的更加舒適。

相關(guān)軟件 版本說明 下載地址

Machining數(shù)控仿真軟件

最新版 查看

KiCad

官方版 64位 查看

LinpressNX沖模設(shè)計軟件

正式版2.0 查看

EWB電子電路設(shè)計軟件

官方版5.0 查看

新功能

1、采用 Spectra-Q 引擎提高您的設(shè)計效能

了解新引擎怎樣減少設(shè)計迭代和編譯,改變了 FPGA 設(shè)計效能的未來。

2、背景知識

現(xiàn)在可以下載新的背景知識,了解 Spectra-Q? 引擎的詳細(xì)信息。了解新引擎怎樣在設(shè)計規(guī)劃和實施的所有階段提供了更多的控制功能和預(yù)測功能。您還將了解到 Spectra-Q 不僅縮短了編譯時間,而且還減少了設(shè)計迭代的總次數(shù),因此成功的解決了設(shè)計效能問題。

3、更短的編譯時間

Spectra-Q 具有以下特性,編譯時間和設(shè)計迭代速度提高了 8 倍,促進(jìn)產(chǎn)品更迅速面市:

·利用當(dāng)今的多核工作站,算法速度更快 (綜合、布局、布線、時序分析,以及物理綜合)

·漸進(jìn)式流程支持設(shè)計人員重新進(jìn)入編譯階段,逐步優(yōu)化各個設(shè)計部分,顯著縮短了設(shè)計迭代時間

·快速重新編譯特性重新使用了綜合和布局布線信息,流暢的處理小的漸進(jìn)式設(shè)計修改,預(yù)綜合 HDL 修改的編譯速度提高了 3 倍,后適配 SignalTap® II 邏輯分析器修改的編譯速度提高了4倍

·分布式編譯支持您對設(shè)計進(jìn)行劃分,在服務(wù)器群的多臺計算機上進(jìn)行并行編譯,極大的縮短了編譯總時間

4、更少的設(shè)計迭代

Spectra-Q 引擎所含有的工具和功能減少了完成 FPGA 和 SoC 設(shè)計所需的設(shè)計迭代次數(shù)。

·BluePrint 平臺設(shè)計者 — BluePrint 平臺設(shè)計者利用 Spectra-Q 新引擎來探查器件外設(shè)體系結(jié)構(gòu),高效的分配接口。BluePrint 實時進(jìn)行適配以及合法檢查,防止了非法引腳分配,避免了復(fù)雜的錯誤消息,也不需要等待全編譯,I/O 設(shè)計速度提高了 10 倍。詳細(xì)了解·使用 BluePrint 平臺設(shè)計者 加速您的 I/O 設(shè)計。

·混合布局器 — Spectra-Q 引擎還支持混合布局新特性,使用了先進(jìn)的布局算法加速邏輯總體布局。混合布放器結(jié)合分析和高級退火技術(shù),提高了結(jié)果質(zhì)量,降低了種子噪聲,從而加速了時序收斂。

5、更快的設(shè)計輸入

還為硬件、軟件和數(shù)字信號處理 (DSP) 設(shè)計人員提供了 Spectra-Q 引擎快速跟蹤設(shè)計輸入功能。通過多個設(shè)計輸入方法,設(shè)計人員采用自己喜歡的設(shè)計環(huán)境,更高效的針對 FPGA 進(jìn)行設(shè)計:

·基于 C 或者 C++ — Spectra-Q 引擎支持為高級綜合提供的 A++ 新編譯器,從 C 或者 C++ 語言中建立知識產(chǎn)權(quán) (IP) 內(nèi)核,通過快速仿真和 IP 生成功能大幅度提高了效能。

·基于 C (OpenCL) — 軟件開發(fā)人員可以使用熟悉的基于C的設(shè)計流程和 面向 OpenCL 的 英特爾® SDK。SDK 提供軟件編程模型,抽象出傳統(tǒng)的 FPGA 硬件設(shè)計流程。

·基于模型 — DSP Builder 工具 支持基于模型的設(shè)計流程:您直接在 Simulink 軟件中,從您的 DSP 算法中生成 HDL。

·基于 RTL — Quartus Prime 軟件支持所有標(biāo)準(zhǔn)語言,包括 SystemVerilog 和 VHDL-2008。

6、為 Stratix 10 FPGA 和 SoC 提供 Spectra-Q 引擎

Stratix 10 FPGA 和 SoC 等下一代具有數(shù)百萬邏輯單元 (LE) 的器件的 FPGA 設(shè)計軟件需要新方法。Spectra-Q 引擎為 Quartus Prime 軟件提供支持,提高 Stratix 10 器件的 設(shè)計效能,促進(jìn)產(chǎn)品及時面市。

Stratix 10 FPGA 和 SoC 硬件實現(xiàn)了創(chuàng)新,特別是其靈活的模塊化體系結(jié)構(gòu),滿足了真正的分層設(shè)計需求。與 Spectra-Q 引擎一起優(yōu)化而顯著提高效能的關(guān)鍵特性包括:

·新的 HyperFlex 內(nèi)核體系結(jié)構(gòu),互聯(lián)結(jié)構(gòu)上遍布寄存器,性能比前幾代 FPGA 提高了 2 倍

·可編程時鐘樹綜合

·采用基于扇區(qū)的方法對器件進(jìn)行配置

·Spectra-Q 引擎發(fā)揮這種靈活性和模塊化的優(yōu)勢,極大的減少了設(shè)計迭代次數(shù),增強了設(shè)計重用,方便了體系結(jié)構(gòu)探查和規(guī)劃。

7、使用Spectra-Q硬劃分進(jìn)行IP集成演示

Spectra-Q引擎為IP重用提供了強大的新功能。例如,F(xiàn)PGA含有高速I/O接口,以極高的數(shù)據(jù)速率向FPGA架構(gòu)傳送數(shù)據(jù)。如果I/O至架構(gòu)傳送時序能夠成功的收斂,作為單獨的數(shù)據(jù)庫——“硬劃分”存儲,那么將有利于縮短產(chǎn)品面市時間。這一數(shù)據(jù)庫保持不變,而FPGA架構(gòu)中設(shè)計的其他部分進(jìn)行綜合、布局和布線的多次修訂。下面的視頻演示了怎樣在Quartus Prime Pro版軟件中作為設(shè)計硬劃分來建立并重用I/O至架構(gòu)傳送,該版軟件是由Spectra-Q引擎支持的。

Quartus II軟件特色

Quartus II提供了完全集成且與電路結(jié)構(gòu)無關(guān)的開發(fā)包環(huán)境,具有數(shù)字邏輯設(shè)計的全部特性,包括:

1、可利用原理圖、結(jié)構(gòu)框圖、VerilogHDL、AHDL和VHDL完成電路描述,并將其保存為設(shè)計實體文件;

2、芯片(電路)平面布局連線編輯;

3、LogicLock增量設(shè)計方法,用戶可建立并優(yōu)化系統(tǒng),然后添加對原始系統(tǒng)的性能影響較小或無影響的后續(xù)模塊;

4、功能強大的邏輯綜合工具;

5、完備的電路功能仿真與時序邏輯仿真工具;定時/時序分析與關(guān)鍵路徑延時分析;可使用SignalTap II邏輯分析工具進(jìn)行嵌入式的邏輯分析;

6、支持軟件源文件的添加和創(chuàng)建,并將它們鏈接起來生成編程文件;

7、使用組合編譯方式可一次完成整體設(shè)計流程;

8、自動定位編譯錯誤;

9、高效的期間編程與驗證工具;

10、可讀入標(biāo)準(zhǔn)的EDIF網(wǎng)表文件、VHDL網(wǎng)表文件和Verilog網(wǎng)表文件;

11、能生成第三方EDA軟件使用的VHDL網(wǎng)表文件和Verilog網(wǎng)表文件。

Quartus II安裝步驟

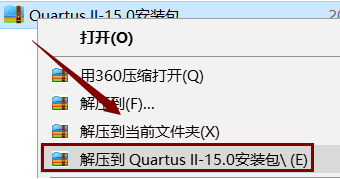

1. 鼠標(biāo)右擊壓縮包選擇解壓

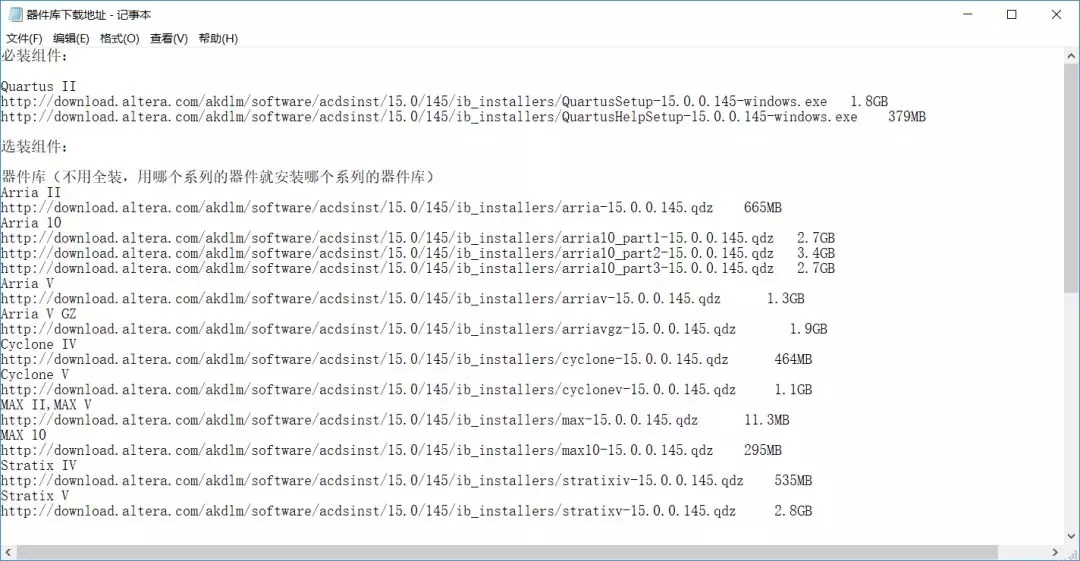

2. 打開“器件庫下載地址”文件,根據(jù)自己需求下載自己所需文件。

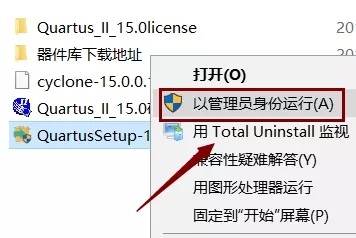

3. 右擊安裝包,選擇“以管理員身份運行”。

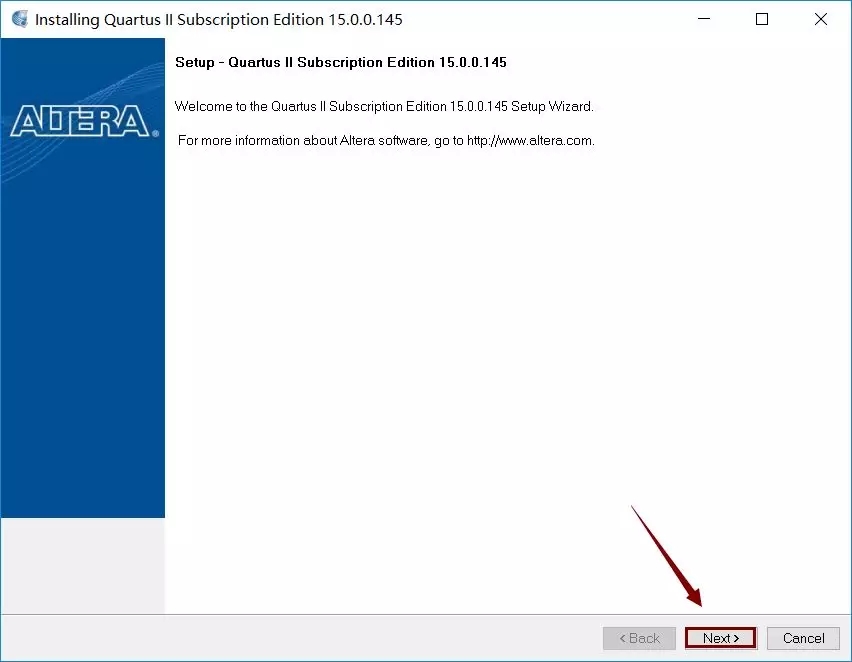

4. 歡迎使用Quartus II軟件,點擊“Next”。

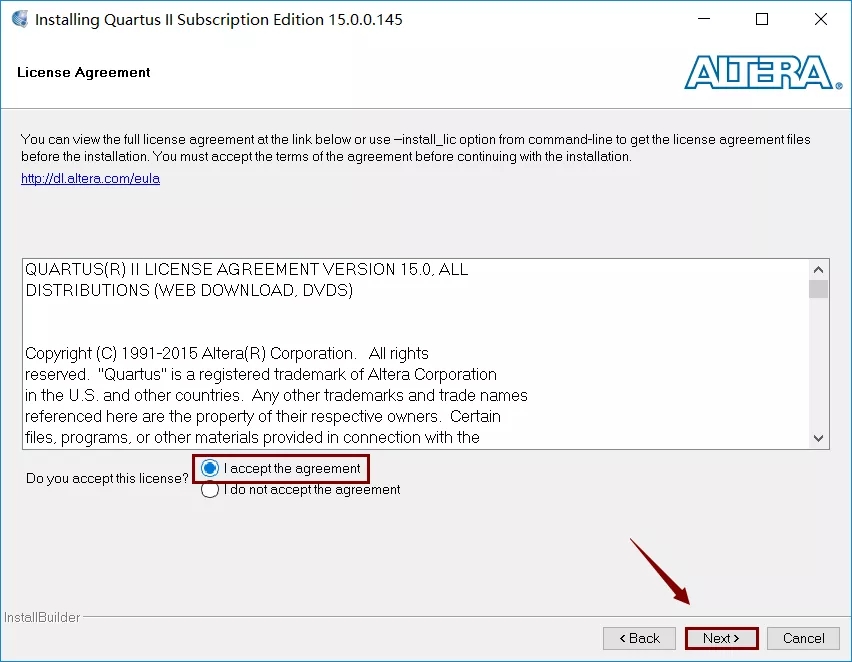

5. 點擊“I accept”選擇同意軟件許可協(xié)議,然后點擊“Next”。

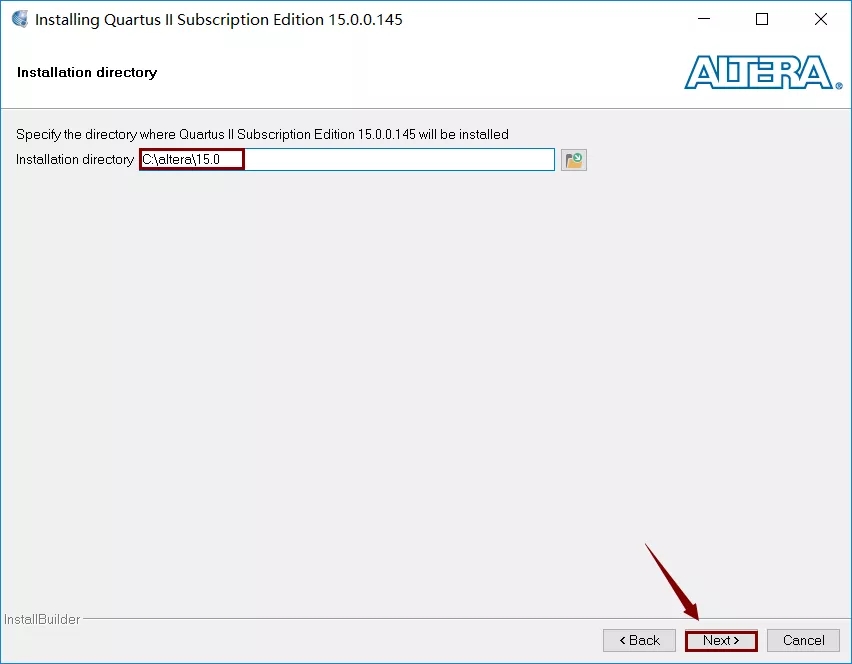

6. 選擇你要安裝的路徑,但請注意不要選擇帶有中文路徑安裝

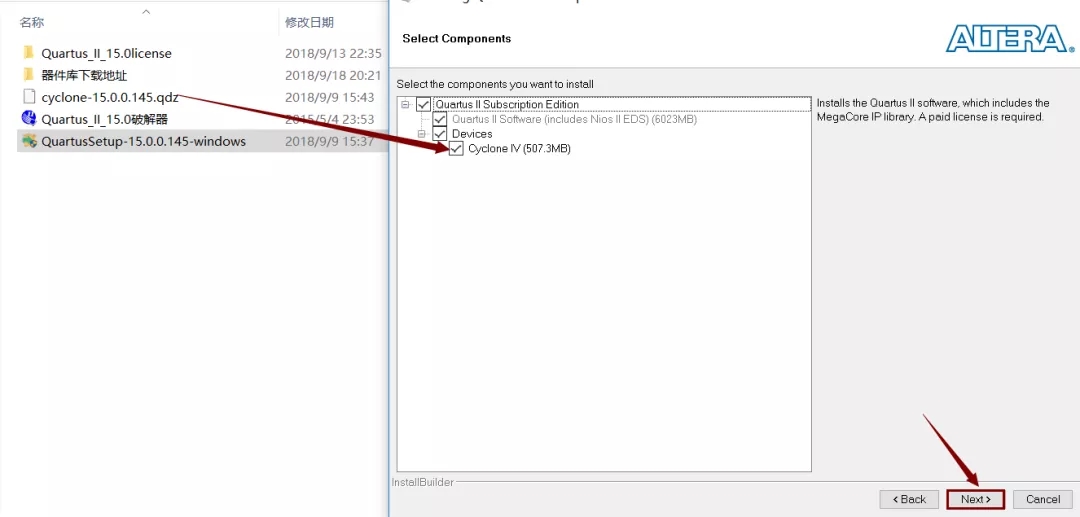

7. 選擇需要安裝的器件庫,注意只有下載了庫文件才能安裝

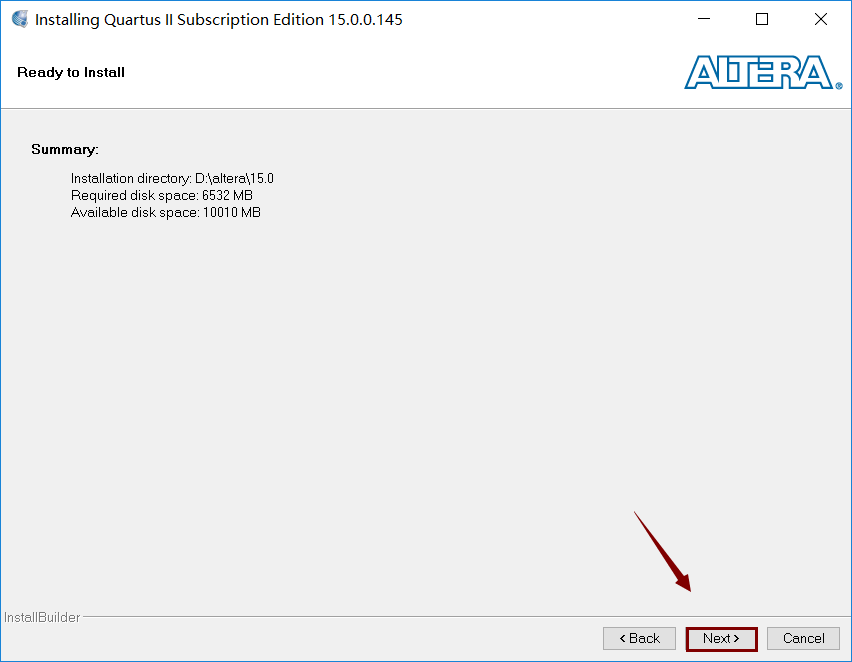

8. 點擊“Next”開始安裝。

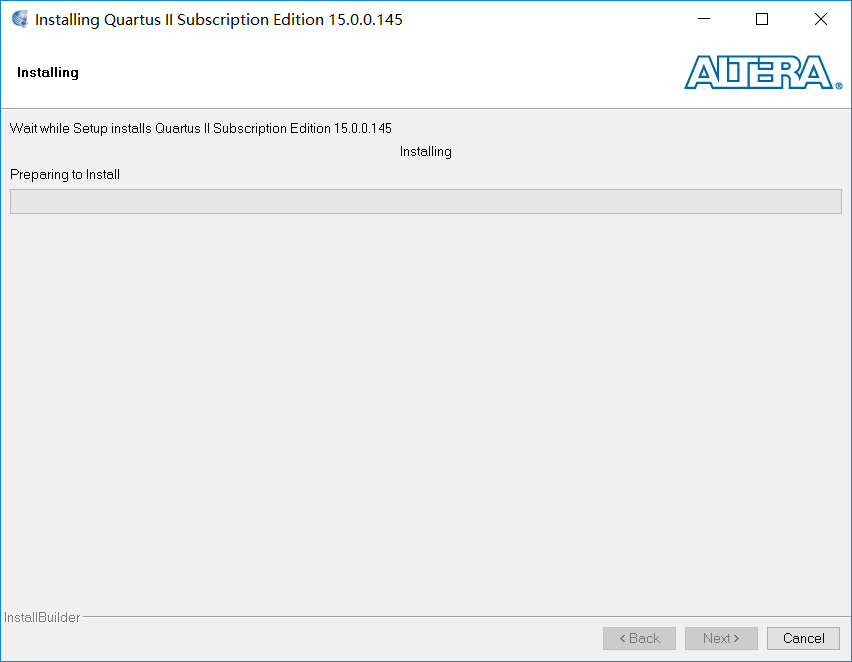

9. 軟件正在安裝中,請等待

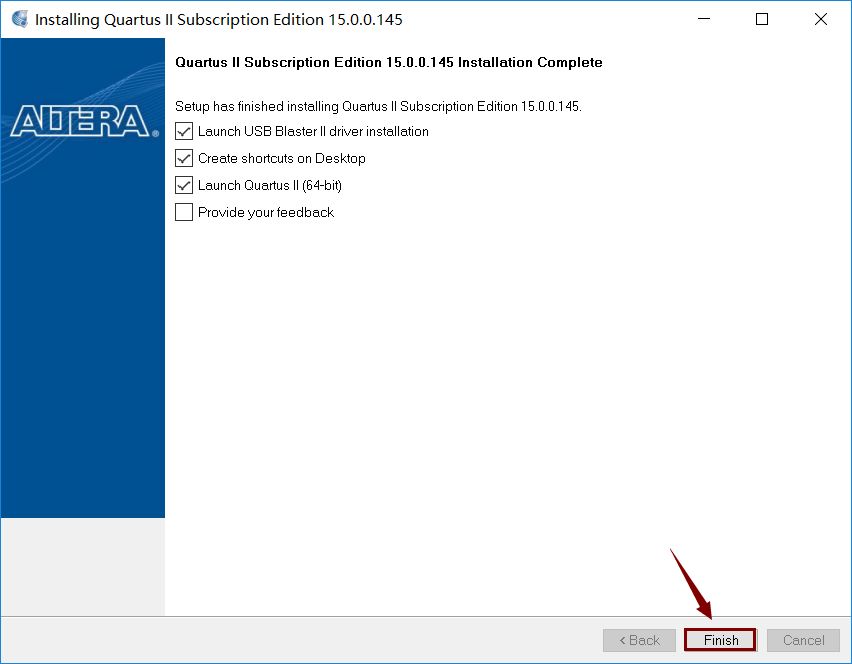

10. 按默認(rèn)選項,點擊“Finish”。

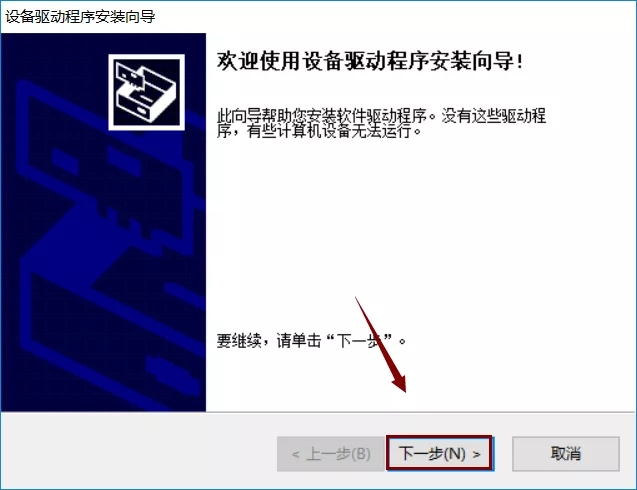

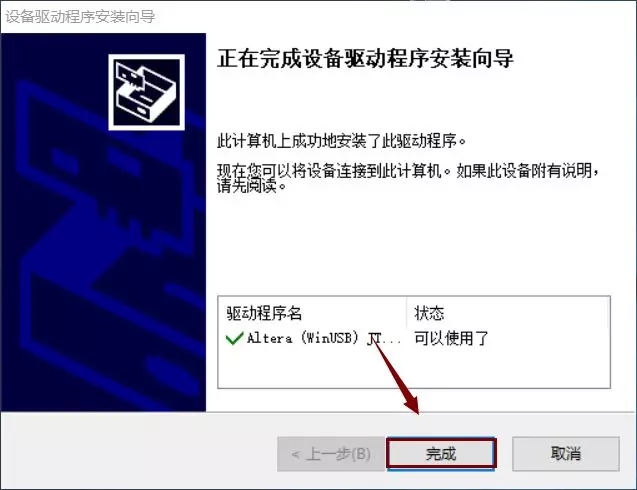

11. 點擊“下一步”繼續(xù)。

12. 點擊“安裝”驅(qū)動。

13. 點擊“完成”。

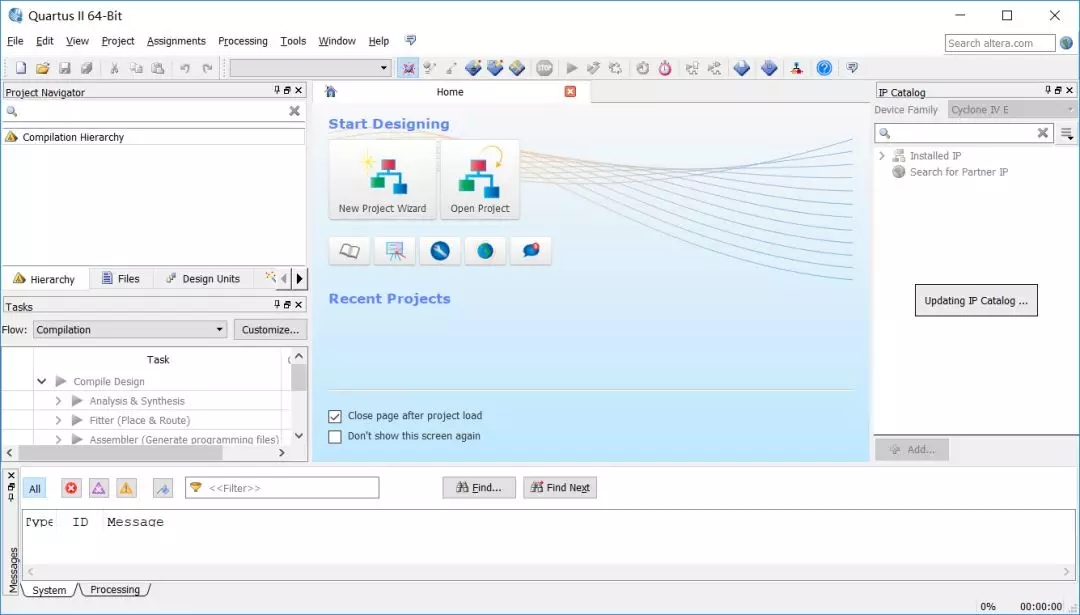

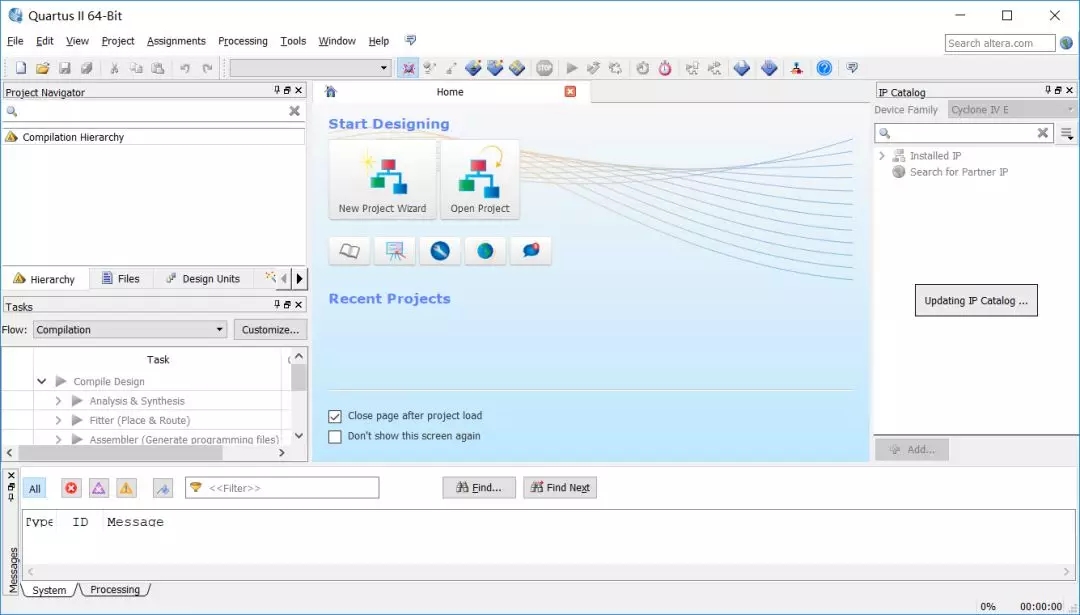

14.軟件安裝完成,打開軟件界面如下

使用方法

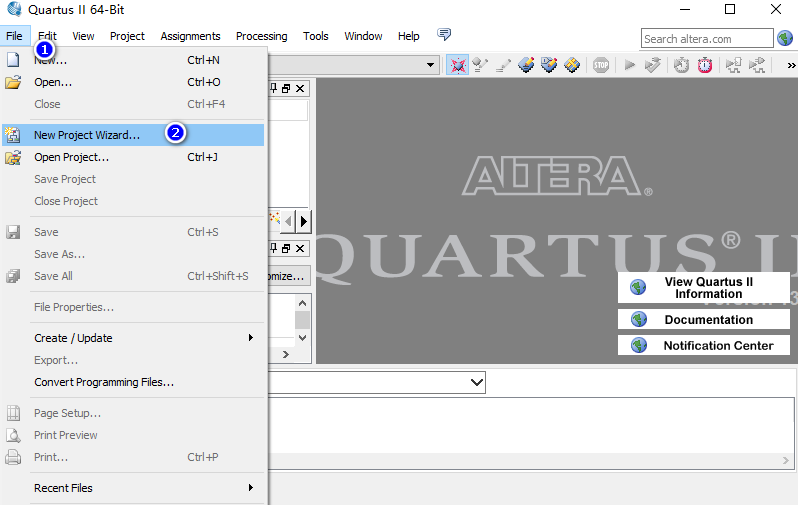

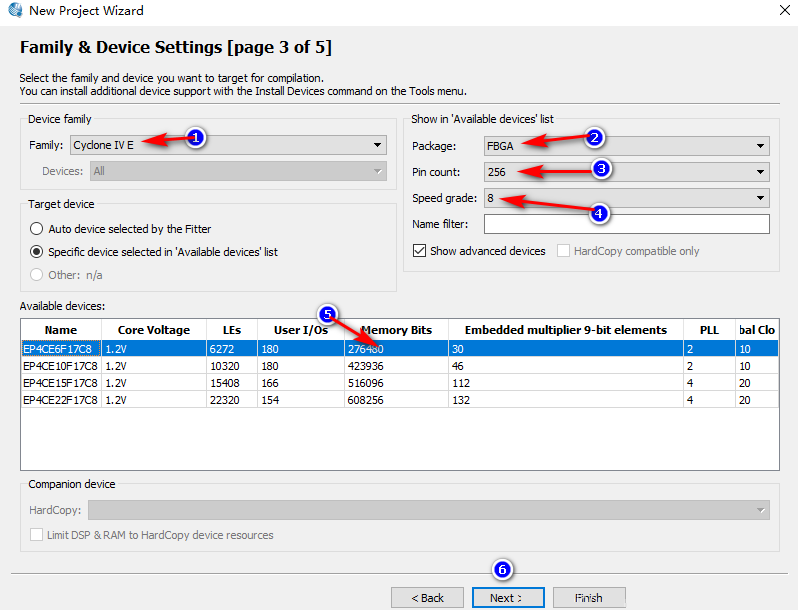

打開軟件,點擊“File——New Project Wizard...”新建一個項目

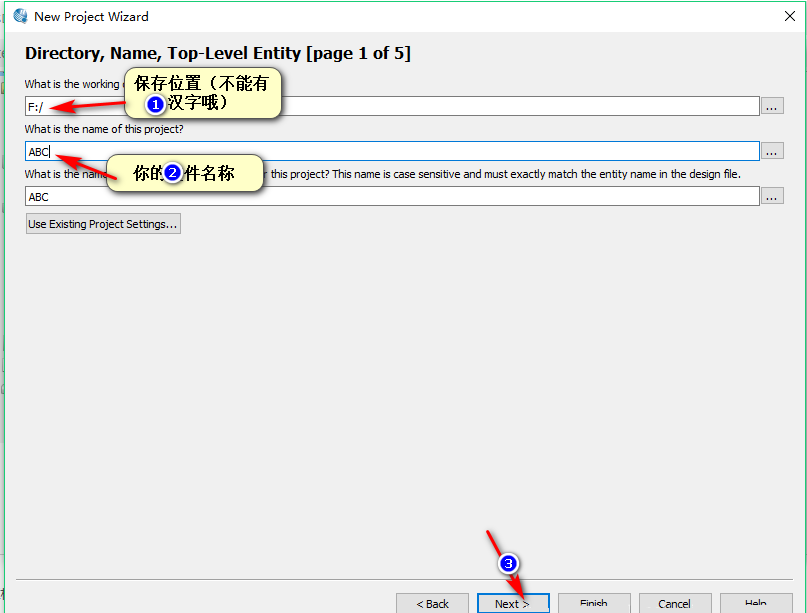

這里會彈出來一個框,然后點擊“next”得到下面這個圖

這里根據(jù)圖示選擇后點擊“next”,都需要點一下哦

全部設(shè)置完成后點擊“finsh”

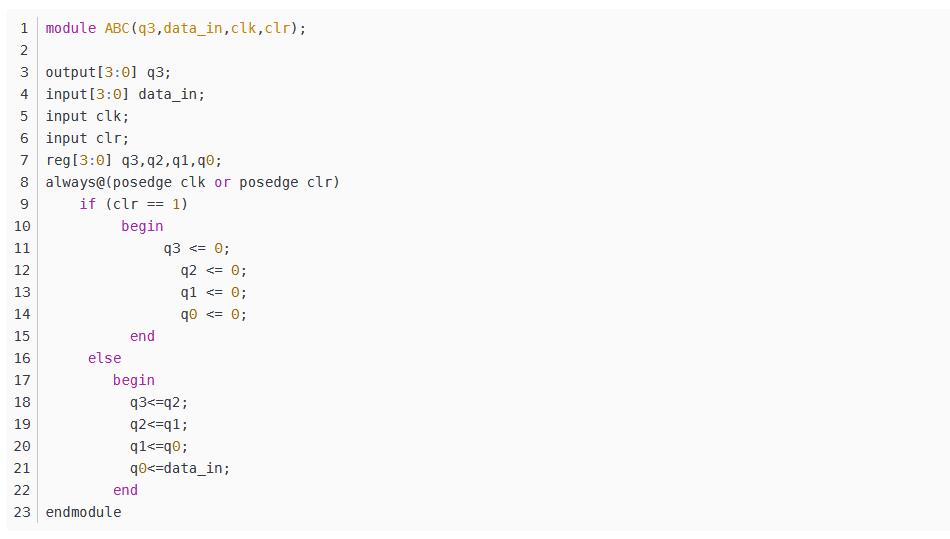

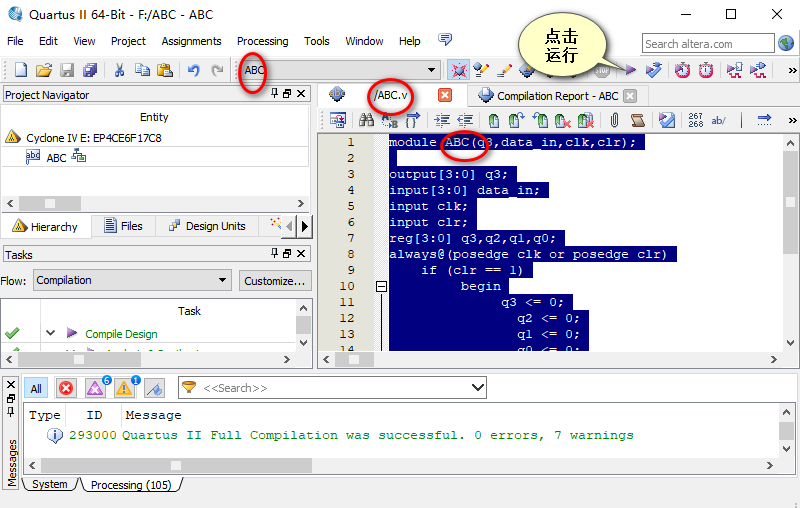

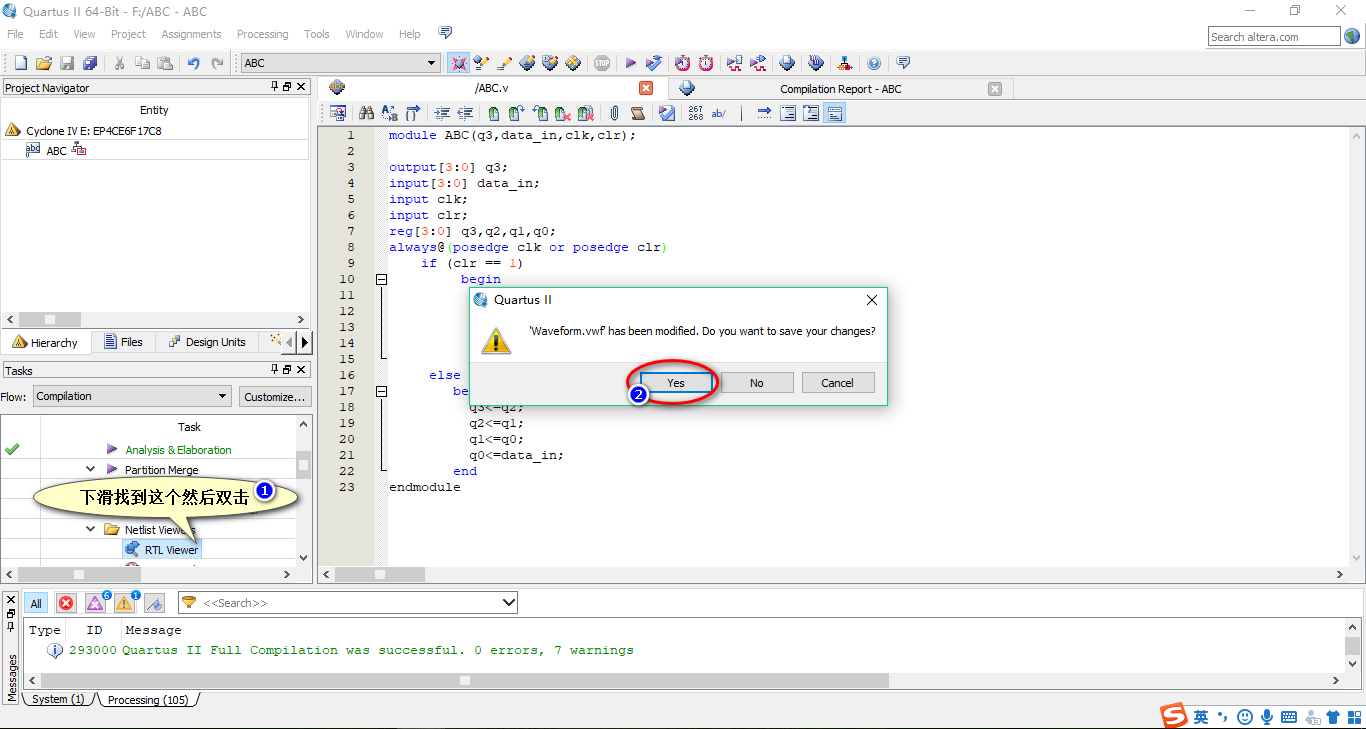

把你的代碼寫入新建的文件當(dāng)中,如上是我的代碼,注意代碼的名稱要和你的文件名稱一樣,否則會有錯誤

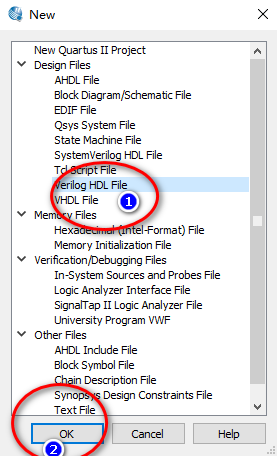

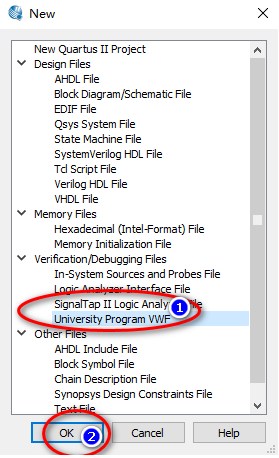

運行成功后,我們開始調(diào)波形圖,如下圖點擊file→new根據(jù)圖示操作

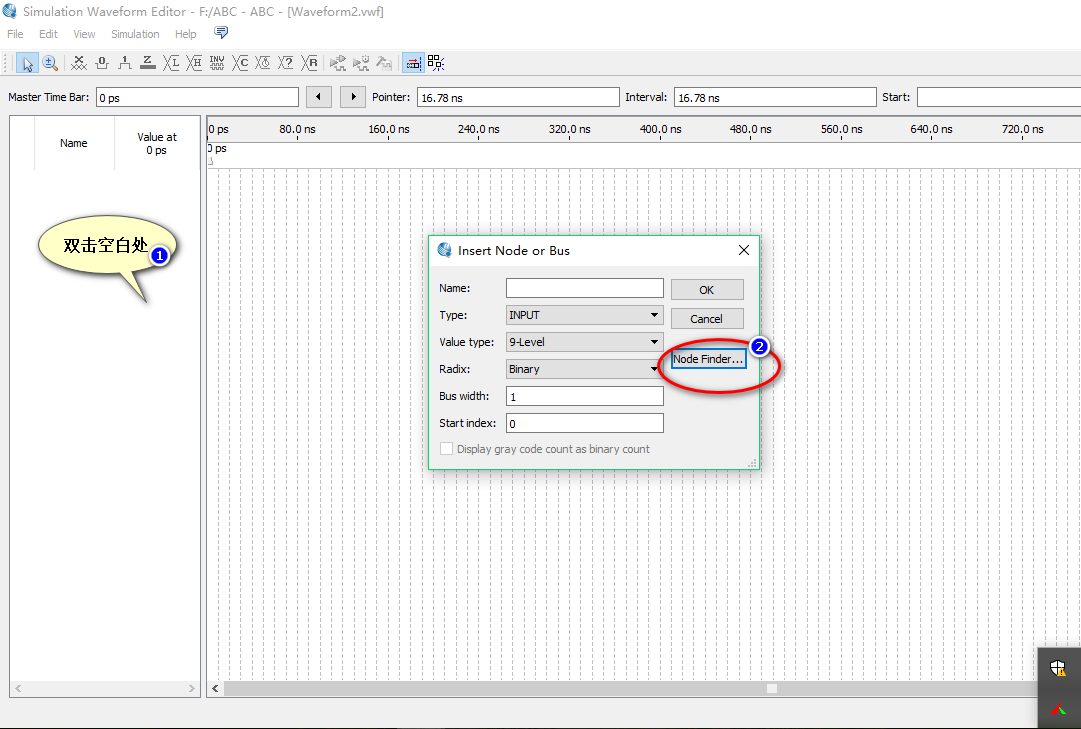

然后再雙擊圖示空白處

之后點擊“ok”

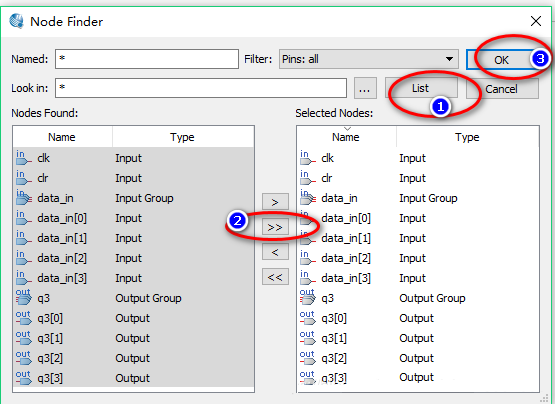

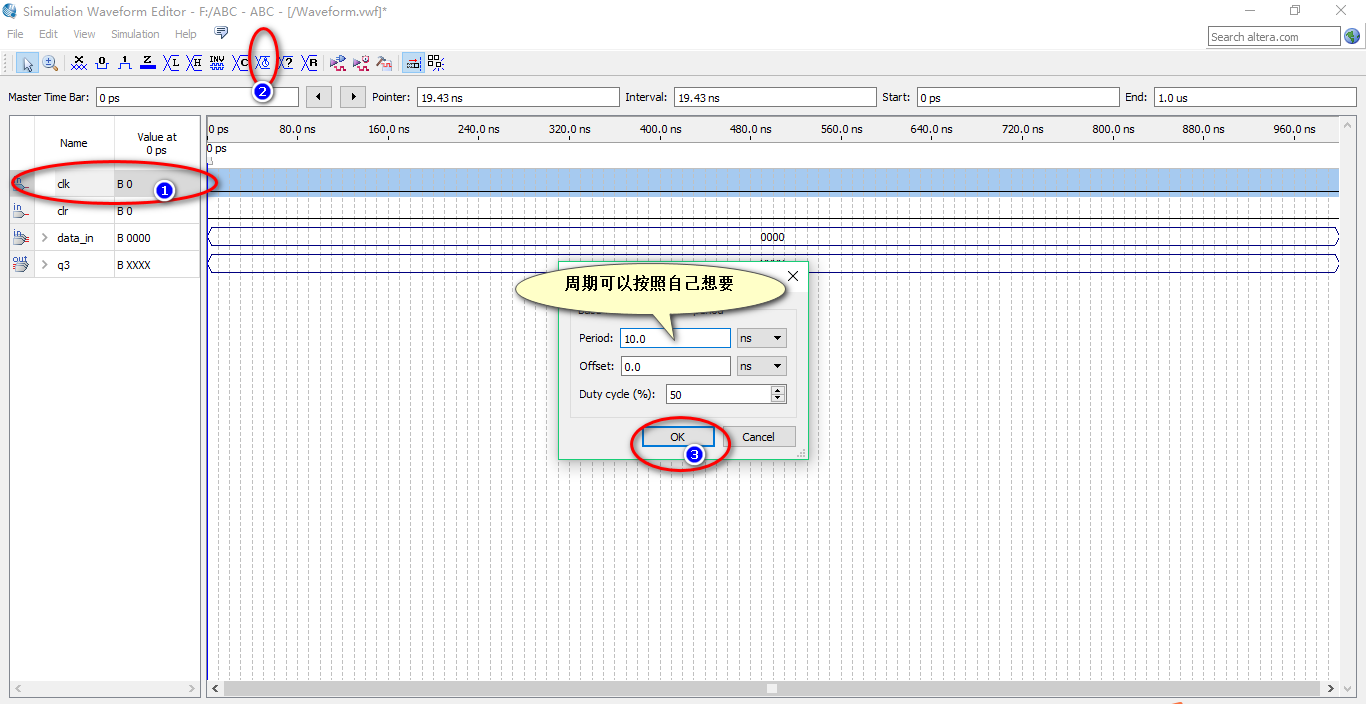

上圖①處的下面幾個一次按照上面的順序就可以出圖了

然后在出仿真圖,回到最開始的頁面

軟件會自動彈出保存框,不要改變位置點擊“保存”即可

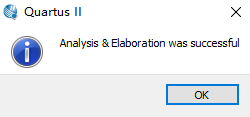

最高點擊“OK”就保存成功了

小編寄語

百度網(wǎng)盤提取碼:4hmd

下載地址

- Pc版

網(wǎng)友評論